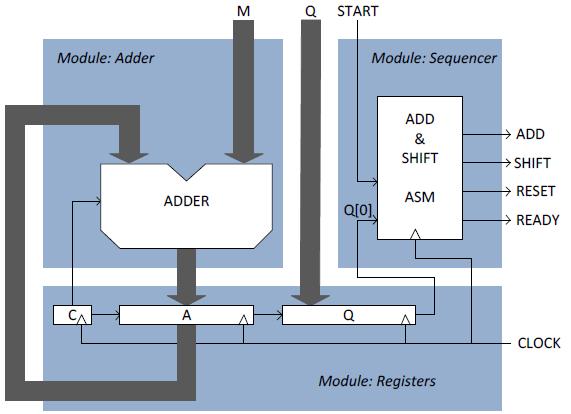

The first time I wrote a design which was synthesised and tested on hardware. Using a MachXO development board (Lattice semiconductor) I constructed a 'shift and add' multiplier. This trades off execution time for design size by putting numbers into registers and shifting to give a multiplication of two. These are then added to a running total (or not) to give multiplication but any possible number. 4-bits is rather trivial but still an interesting topic which took me a while to grasp the motivation for the design.

Find the report here for which I received 70% and a zip file of code here.