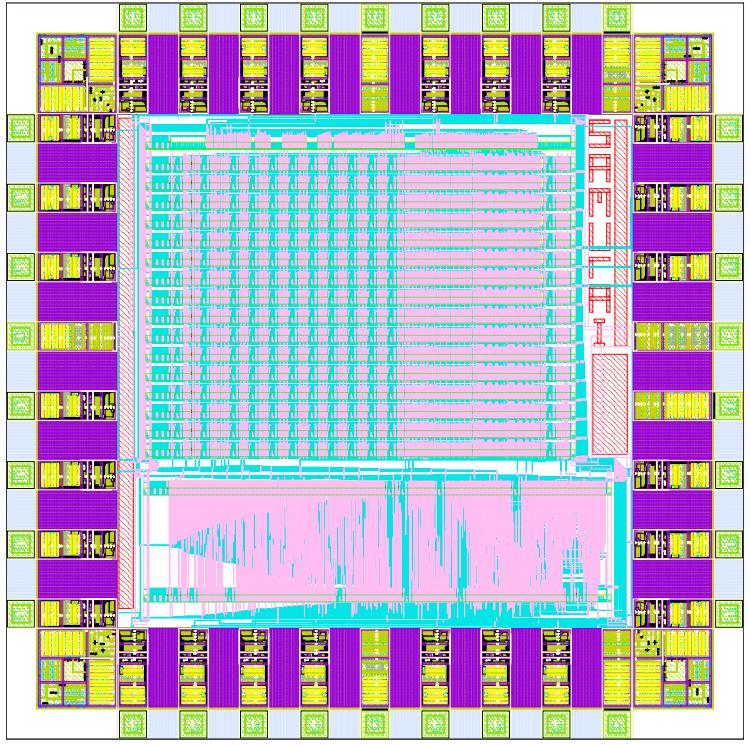

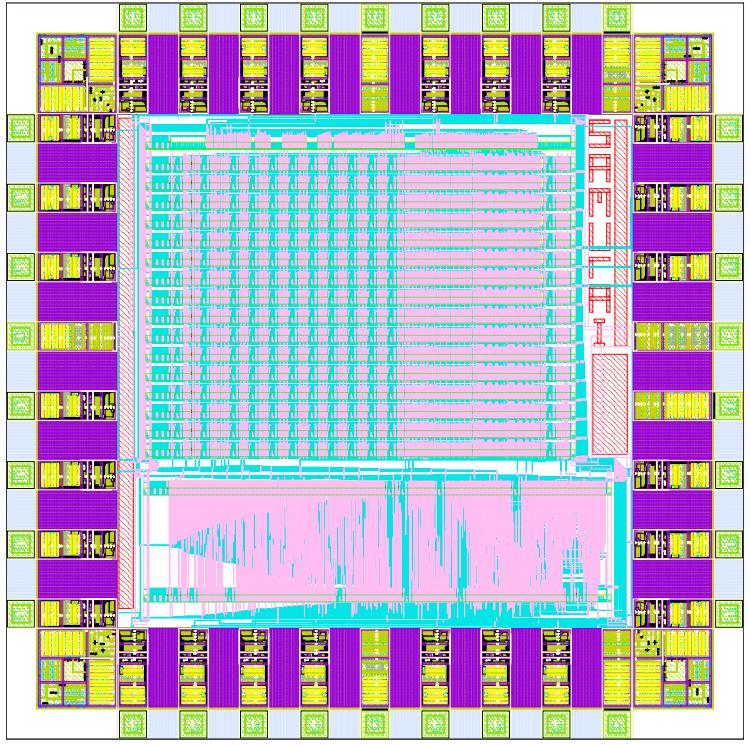

SAMURAI: Sixteen bit Arm and Mips Unified Risc Architecture with Interrupts

Samurai is a novel microprocessor unit in full custom 0.35um CMOS.

All cells were created by myself along with three team members

The reaming work was done by myself and two of the original members with a fourth external member.

The processor was the only one produced, out of the ten teams made from that year of students, to implement interrupts.

Only one is fabricated each year and we came in second place to a team with a much smaller design (our 4.61 sq mm against their 2.79 sq mm).

They also implemented a multiply instruction whereas we chose to invest our efforts in a multi-bit shifter and interrupts.

Our design is ready for fabrication but unfortunately will remain just a design.

A large shot of the floor plan lives on my bedroom wall.

Myself and my team mates are very proud.

We have a verified our custom instruction set and in the code you will also find an assembler.

Maybe one day I'll port a C complier for our chip and save up to send it off for fabrication.

Who knows, maybe on day home fabs will be just as common as 3D printers?

Subroutines: My initial research report.

Report: Submitted to the University